Product Descriptions

The MAX 7000 family of high-density, high-performance PLDs is based on Altera’s second-generation MAX architecture.

Fabricated with advanced CMOS technology, the EEPROM-based MAX 7000 family provides 600 to 5,000 usable gates, ISP, pin-to-pin delays as fast as 5 ns, and counter speeds of up to 175.4 MHz

Product Features

■ High-performance, EEPROM-based programmable logic devices (PLDs) based on second-generation MAX? architecture

■ 5.0-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface available in MAX 7000S devices

– ISP circuitry compatible with IEEE Std. 1532

■ Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S devices

■ Built-in JTAG boundary-scan test (BST) circuitry in MAX7000S devices with 128 or more macrocells

■ Complete EPLD family with logic densities ranging from 600 to 5,000 usable gates (see Tables 1 and 2)

■ 5-ns pin-to-pin logic delays with up to 175.4-MHz counter frequencies (including interconnect)

■ PCI-compliant devices available

■ Open-drain output option in MAX 7000S devices

■ Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls

■ Programmable power-saving mode for a reduction of over 50% in each macrocell

■ Configurable expander product-term distribution, allowing up to 32 product terms per macrocell

■ 44 to 208 pins available in plastic J-lead chip carrier (PLCC), ceramic pin-grid array (PGA), plastic quad flat pack (PQFP), power quad flat

pack (RQFP), and 1.0-mm thin quad flat pack (TQFP) packages

■ Programmable security bit for protection of proprietary designs

■ 3.3-V or 5.0-V operation

– MultiVoltTM I/O interface operation, allowing devices to interface with 3.3-V or 5.0-V devices (MultiVolt I/O operation is not available in 44-pin packages)

– Pin compatible with low-voltage MAX 7000A and MAX 7000B devices

■ Enhanced features available in MAX 7000E and MAX 7000S devices

– Six pin- or logic-driven output enable signals

– Two global clock signals with optional inversion

– Enhanced interconnect resources for improved routability

– Fast input setup times provided by a dedicated path from I/O pin to macrocell registers

– Programmable output slew-rate control

■ Software design support and automatic place-and-route provided by Altera’s development system for Windows-based PCs and Sun

SPARCstation, and HP 9000 Series 700/800 workstations

Specifications

| Part# | EPM7064SLI44-7N |

| Category | Integrated Circuits (ICs) |

| Embedded | |

| CPLDs (Complex Programmable Logic Devices) | |

| Mfr | ALTERA |

| Series | MAX? 7000S |

| Package | REEL |

| Product Status | Obsolete |

| DigiKey Programmable | Verified |

| Programmable Type | In System Programmable |

| Delay Time tpd(1) Max | 7.5 ns |

| Voltage Supply - Internal | 4.5V ~ 5.5V |

| Number of Logic Elements/Blocks | 4 |

| Number of Macrocells | 64 |

| Number of Gates | 1250 |

| Number of I/O | 36 |

| Operating Temperature | -40°C ~ 85°C (TA) |

| Mounting Type | Surface Mount |

| Package / Case | 44-LCC (J-Lead) |

| Supplier Device Package | 44-PLCC (16.59x16.59) |

| Base Product Number | EPM7064 |

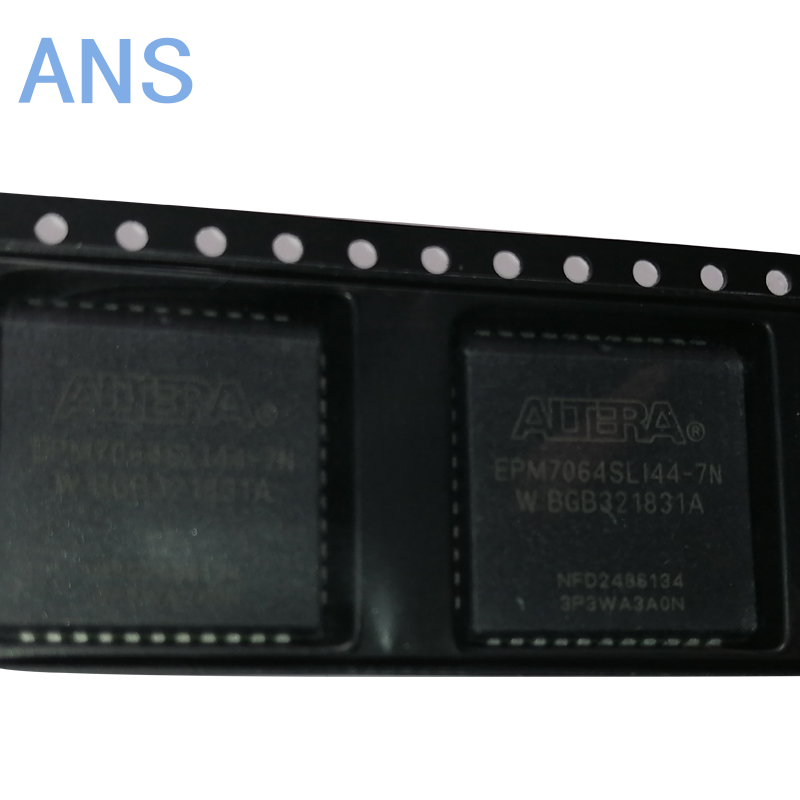

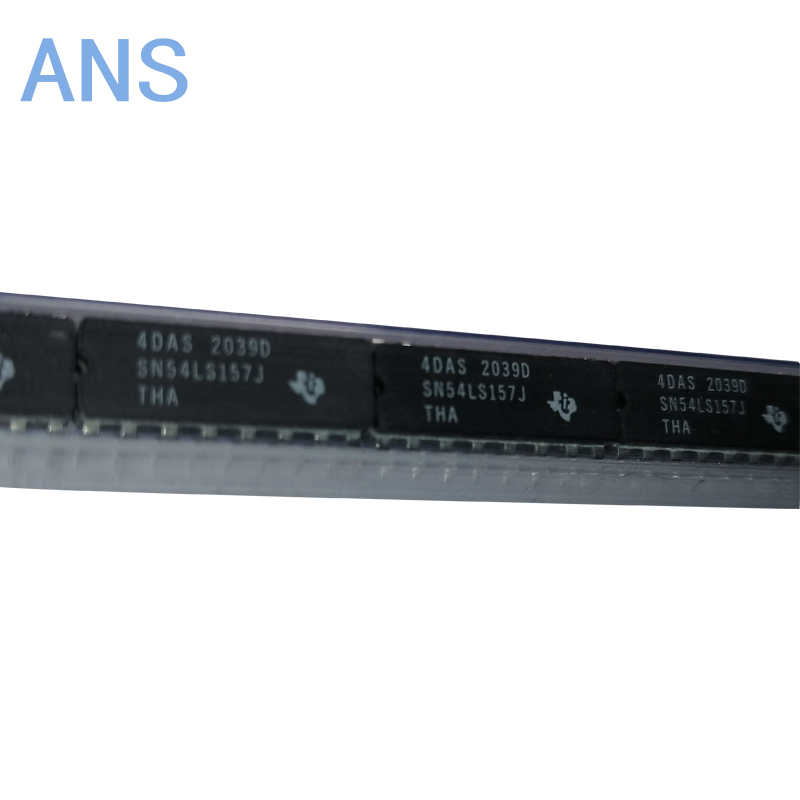

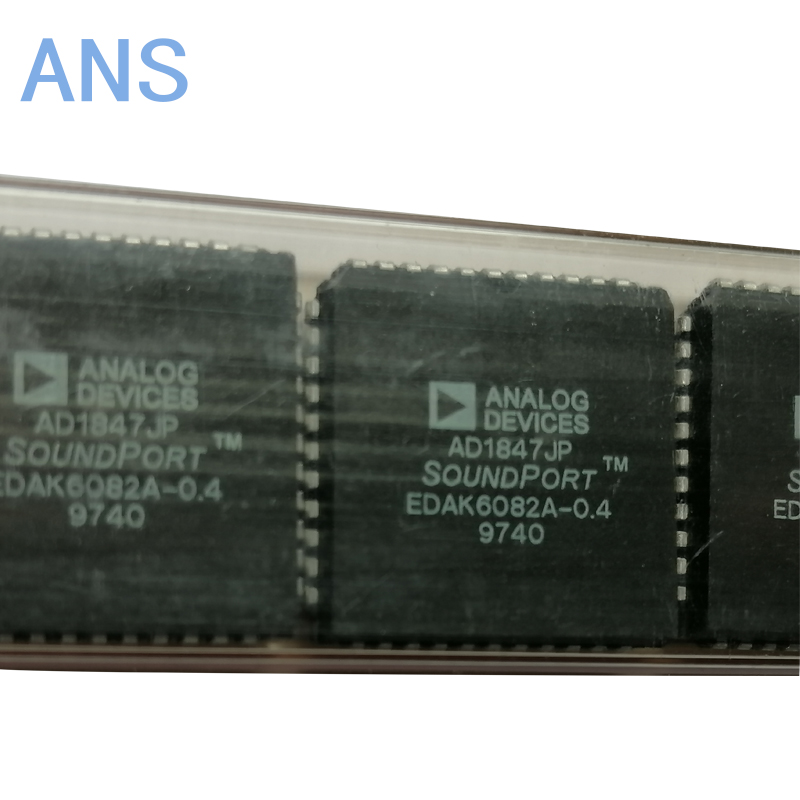

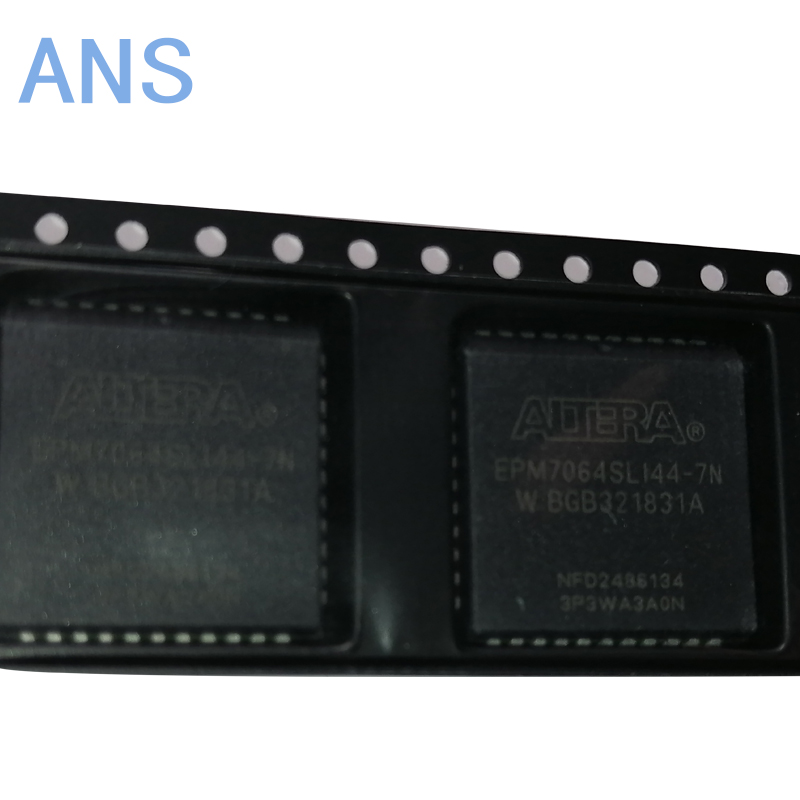

Actual product photos

Payment&Transportation

Official Certificate&Certificate

Multiple product supply

Company office environment

Warehouse Real Shot

Standard packaging

We also provide :

| Part No | Manufacturer | Date Code | Quantity | Description |

| LM22676ADJ | NS | 19+ | 250 | SOP8 |

| TPS562201DDCR | TI | 22+ | 795500 | SOT23-6 |

| NJG1806K75 | JRC | 22+ | 500000 | DFN6 |

| TLV74318PDQNR | TI | 22+ | 402000 | X2SON-4 |

| NJG1801K75 | JRC | 22+ | 300000 | SMD |

| NJG1804K64 | JRC | 22+ | 300000 | DFN8 |

| LM27761DSGR | TI | 22+ | 151000 | WSON8 |

| TLV62565DBVR | TI | 22+ | 138000 | SOT23-5 |

| TPS613222ADBVR | TI | 22+ | 108000 | SOT23-5 |

| LNK625DG-TL | POWER | 22+ | 100000 | SOP-8 |

| OPA4322AIPWR | TI | 22+ | 100000 | TSSOP14 |

| TLV75528PDRVR | TI | 22+ | 99000 | WSON-6 |

| TPS7A2025PDQNR | TI | 22+ | 78500 | X2SON-4 |

| TLV62568DBVR | TI | 22+ | 72000 | SOT23-5 |

| STM32L051K8U6TR | ST | 22+ | 60000 | QFN32 |

| SKY66421-11 | SKYWORKS | 22+ | 56500 | QFN16 |

| TPS7A1111PDRVR | TI | 22+ | 54000 | WSON6 |

| TLV62569PDDCR | TI | 22+ | 52000 | SOT23-6 |

| TLV62569DBVR | TI | 22+ | 48000 | SOT23-5 |

| TPS23753APWR | TI | 22+ | 40000 | TSSOP14 |

| NB691GG-Z | MPS | 22+ | 30000 | QFN |

| SN74AHC1G02DBVR | TI | 22+ | 27939 | SOT-23 |

| TPS63000DRCR | TI | 22+ | 23238 | VSON10 |

| TLV75533PDRVR | TI | 22+ | 21500 | WSON6 |

| NB687BGQ-Z | MPS | 22+ | 20000 | QFN |

| A3916GESTR-T-1 | ALLEGRO | 22+ | 17150 | QFN-20 |

| TPS62135RGXR | TI | 22+ | 15000 | VQFN11 |

| TLE2022AMDR | TI | 0803+ | 12500 | SOP8 |

| TPS23756PWPR | TI | 22+ | 12000 | HTSSOP-20 |